Paper 62 Entered: April 14, 2016

## UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

LG ELECTRONICS, INC., Petitioner,

v.

ATI TECHNOLOGIES ULC, Patent Owner.

Case IPR2015-00325 Patent 7,742,053 B2

Before JONI Y. CHANG, BRIAN J. McNAMARA, and RAMA G. ELLURU, *Administrative Patent Judges*.

CHANG, Administrative Patent Judge.

FINAL WRITTEN DECISION 35 U.S.C. § 318(a) and 37 C.F.R. § 42.73

#### I. INTRODUCTION

LG Electronics, Inc. ("LG") filed a Petition requesting an *inter partes* review of claims 1, 2, and 5–7 ("the challenged claims") of U.S. Patent No. 7,742,053 B2 (Ex. 1001, "the '053 patent"). Paper 2 ("Pet."). Patent Owner, ATI Technologies ULC ("ATI"), filed a Preliminary Response. Paper 12 ("Prelim. Resp."). Upon consideration of the Petition and Preliminary Response, we instituted this trial as to claims 1, 2, and 5–7 of the '053 patent on June 15, 2015. Paper 13 ("Dec.").

Subsequent to institution, ATI filed a Patent Owner Response (Papers 21, 22, "PO Resp."); LG filed a Reply to the Patent Owner Response (Papers 33, 34, "Reply"); and ATI filed a sur-reply to LG's Reply with respect to the antedating issue (Papers 39, 40).<sup>1</sup> An oral hearing was held on February 10, 2016.<sup>2</sup>

We have jurisdiction under 35 U.S.C. § 6(c). This Final Written Decision is issued pursuant to 35 U.S.C. § 318(a). For the reasons discussed herein, and in view of the record in this trial, we determine that LG has shown by a preponderance of the evidence that claims 1, 2, and 5–7 of the '053 patent are unpatentable.

<sup>&</sup>lt;sup>1</sup> The parties filed a confidential version and a redacted version of their papers. The Decisions denying the parties' Motions to Seal these documents and supporting evidence are entered concurrently with this Final Written Decision. Papers 63, 64. The citations to these papers are to the unredacted versions.

<sup>&</sup>lt;sup>2</sup> A transcript of the oral hearing is entered in the record as Paper 61 ("Tr.").

#### A. Related Matter

The '053 patent is asserted in *Advanced Micro Devices, Inc. v. LG Electronics, Inc.*, No. 3:14-cv-01012-SI (N.D. Cal.). Pet. 1.

#### B. The '053 Patent

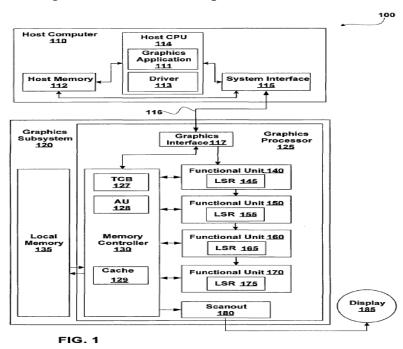

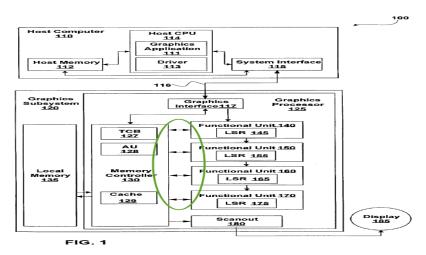

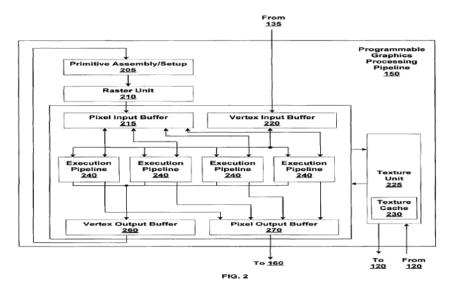

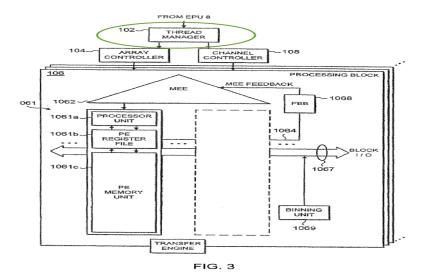

The '053 patent discloses a computer system for multithreaded graphics processing. Ex. 1001, 2:36–41. The system includes a memory device for storing command threads and an arbiter for providing a command thread to a command processing engine, based on a priority scheme. *Id.* at 2:48–52, 3:29–35; *see* Paper 13, 2–3.

#### C. Illustrative Claim

Of the challenged claims, claims 1 and 5 are independent. Claim 2 depends from claim 1, and claims 6 and 7 depend directly from claim 5. Claim 5, reproduced below, is illustrative of the challenged claims.

- 5. A graphics processing system comprising:

- at least one *memory device* comprising a first portion operative to store a plurality of pixel command threads and a second portion operative to store a plurality of vertex command threads;

- an *arbiter*, coupled to the at least one memory device, operable to select a command thread from either of the plurality of pixel command threads and the plurality of vertex command threads; and

- a plurality of *command processing engines*, coupled to the arbiter, each operable to receive and process the command thread.

Ex. 1001, 8:4–15 (emphases added).

# D. Prior Art Relied Upon

LG relies upon the following prior art references:

| Lindholm  | US 7,015,913 B1 | Mar. 21, 2006 | (Ex. 1004) |

|-----------|-----------------|---------------|------------|

| Stuttard  | US 7,363,472 B2 | Apr. 22, 2008 | (Ex. 1005) |

| Moreton   | US 7,233,335 B2 | June 19, 2007 | (Ex. 1006) |

| Whittaker | US 5,968,167    | Oct. 19, 1999 | (Ex. 1007) |

| Kimura    | US 6,105,127    | Aug. 15, 2000 | (Ex. 1008) |

Admitted Prior Art – Figure 1, and the Background of the Invention Section of the '053 patent. Ex. 1001, 1:22–2:6, Fig. 1.

# E. Instituted Grounds of Unpatentability

We instituted this trial based on the following grounds (Dec. 36–37):

| Claims        | Basis    | References                                 |

|---------------|----------|--------------------------------------------|

| 5–7           | § 102(e) | Moreton                                    |

| 1 and 2       | § 103(a) | Moreton and Whittaker                      |

| 1, 2, and 5–7 | § 103(a) | Lindholm in view of the Admitted Prior Art |

| 1, 2, and 5–7 | § 103(a) | Stuttard in view of the Admitted Prior Art |

#### II. ANALYSIS

#### A. Claim Construction

In an *inter partes* review, claim terms in an unexpired patent are given their broadest reasonable construction in light of the specification of the patent in which they appear. 37 C.F.R. § 42.100(b). Under the broadest reasonable interpretation standard, claim terms are given their ordinary and customary meaning as would be understood by one of ordinary skill in the

art in the context of the entire disclosure. *In re Translogic Tech.*, *Inc.*, 504 F.3d 1249, 1257 (Fed. Cir. 2007).

## "command thread"

Each of independent claims 1 and 5 recites "at least one memory device comprising a first portion operative to store a plurality of pixel *command threads* and a second portion operative to store a plurality of vertex *command threads*." Ex. 1001, 7:11–15, 8:5–8 (emphases added). Before institution, ATI urged us to construe "command thread" as "a sequence of commands." Prelim. Resp. 12–13. ATI also argued that a command thread does *not* encompass an *instruction*. *Id*. at 12.

In the Decision on Institution (Dec. 6–7), we noted that the word "command" is used in the Specification of the '053 patent consistent with its plain and ordinary meaning, as including an *instruction*. *See*, *e.g.*, Ex. 1001, 4:21–27; MICROSOFT COMPUTER DICTIONARY 111 (5th ed. 2002) (Ex. 3001) (defining "command" as an "instruction to a computer program that, when issued by the user, causes an action to be carried out"). Notably, the Specification discloses that "[u]pon the execution of the associated *command of the command thread*, the thread is thereupon returned to the station 302 or 304 at the same storage location with its status updated, once all possible sequential *instructions* have been executed." Ex. 1001, 4:21–27 (emphasis added). Dr. Nader Bagherzadeh testifies that, in the context of computer multithreading, a stream of instructions is called a thread. Ex. 1003 ¶ 23–24. This is consistent with the usage of the word "thread" in

the prior art of record. *See, e.g.*, Ex. 1005, 5:19–30. We further note that the plain meaning of "thread," in the context of computer programming, means a process that is part of a larger process or program. MICROSOFT COMPUTER DICTIONARY 518 (5th ed. 2002) (Ex. 3001). We, therefore, disagreed with ATI, in our Decision on Institution, that a command thread does not encompass an instruction, as it would be inconsistent with the term's plain and ordinary meaning. Rather—for purposes of the Decision on Institution—in light of the Specification, we construed the claim term "command thread" to encompass a stream of instructions or a process that is part of a larger process or program. Dec. 6–7.

After institution, ATI does not challenge our claim construction. PO Resp. 30. In fact, ATI's expert, Dr. Andrew Wolfe, testifies that one of ordinary skill in the art would have understood that the term "command thread" requires instructions. Ex. 2151 ¶¶ 57–58, 118. As such, we discern no reason to change our claim construction of "command thread" for this Final Written Decision.

#### "arbiter"

Each of independent claims 1 and 5 recites "an *arbiter*, coupled to the at least one memory device, operable to *select a command thread* from either of the plurality of pixel command threads and the plurality of vertex command threads." Ex. 1001, 7:16–19, 8:9–12.

In its Petition, LG proposes to construe the claim term "arbiter" as "any implementation of hardware and/or software that receives and provides

a thread." Pet. 9. As support, LG cites to the Specification, which explains that an "arbiter may be any implementation of hardware, software or combination thereof such that the arbiter receives the command thread and thereupon provides the command thread to a command processing engine." *Id.* (citing Ex. 1001, 2:48–52).

Before institution, ATI argued that LG's proposed construction "ignores arbitration," and proposed that the claim term "arbiter" should be construed as "a component for picking out a command thread among available pixel and vertex command threads." Prelim. Resp. 10–11. ATI's proposed construction, however, improperly would import other claim language—"picking out a command thread among available pixel and vertex command threads"—into the construction of the claim term "arbiter." Such a construction also would render other claim language superfluous—e.g., "select a command thread from either of the plurality of pixel command threads and the plurality of vertex command threads," recited in claim 5. Moreover, the Specification explains that "arbiter 204 retrieves a command thread via connection 214 and *provides* the retrieved command thread to the command processing engine." Ex. 1001, 3:8–10 (emphasis added). As such, we declined to adopt ATI's proposed construction. Rather—for purposes of the Decision on Institution—in light of the Specification, we construed the claim term "arbiter" as any computer hardware, software, or combination thereof that receives and provides a command thread. Dec. 7– 8. After institution, neither party proffers a different construction for this term. See PO Resp.; Reply. Upon review of this record, we discern no

reason to change our claim construction of "arbiter" for this Final Written Decision.

# "command processing engine"

Claim 5 recites "a plurality of command processing engines, coupled to the arbiter, each operable to receive and process the command thread." Ex. 1001, 8:13–15 (emphasis added). Claims 6 and 7 directly depend from claim 5, and further recite "wherein the plurality of command processing engines comprises at least one arithmetic logic unit" and "at least one texture processing engine," respectively. *Id.* at 8:16–21 (emphases added).

LG proposes to construe "command processing engine" as "any implementation of hardware and/or software that processes commands." Pet. 9. In its Patent Owner Response, ATI asserts that an ordinarily skilled artisan would have understood that the "command processing engine" limitation recited in claim 5 requires *each* command processing engine to be able to process *both* pixel and vertex command threads. PO Resp. 31; Ex. 2151 ¶ 125.

LG disagrees, arguing that the disputed limitation recited in claim 5 merely requires that the command processing engines are capable of processing *either* a pixel command thread *or* a vertex command thread because claim 5 recites "an arbiter . . . operable to select <u>a</u> command thread" and "a plurality of command processing engines . . . each operable to receive and process the command thread." Reply 14 (emphases added by LG).

Upon review of the claim language and Specification, we agree with LG. Nothing in the claim language requires a single command processing engine to be able to process both pixel and vertex command threads.

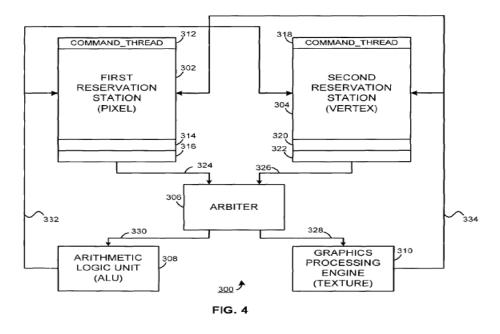

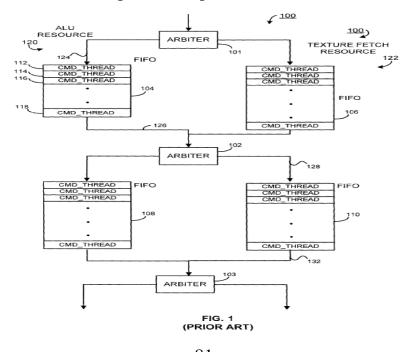

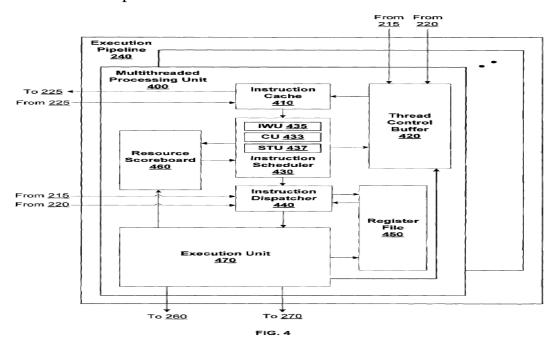

We note that ATI's proposed claim construction essentially requires *each* of the plurality of command processing engines to have the capability to process *all* of the command threads selected by the arbiter—excluding *type-specific* processing engines. The Specification of the '053 patent, however, does not support such a narrow construction. Notably, the Specification discloses that the "command processing engine may be *any suitable engine as recognized by one having ordinary skill in the art* for processing commands, such as a texture engine, an arithmetic logic unit, or any other suitable processing engine." Ex. 1001, 2:59–62 (emphasis added). Additionally, claims 5–7 are directed to the preferred embodiment illustrated in Figure 4 of the '053 patent, which is reproduced below.

As shown in Figure 4, processing system 300 includes first reservation station 302, which contains pixel command threads; second reservation station 304, which contains vertex command threads; arbiter 306; arithmetic logic unit 308; and texture engine 310. *Id.* at 3:62–4:33. The Specification explains that arbiter 306 retrieves pixel command thread 324 and vertex command thread 326 and then provides thread 328, which may be either pixel command thread 324 or vertex command thread 326, to texture engine 310. Id. at 4:28–33. Arbiter 306 further provides the other thread 330 to arithmetic logic unit ("ALU") 308. *Id.* Upon execution of the command, ALU 308 and text engine 310 return command threads 332 and 334 to the appropriate reservation station 302 or 304. *Id.* at 4:34–41. As the Specification explains, multiple *command operations* may be performed by ALU 308 or texture engine 310, but, in order to switch a thread from ALU 308 to texture engine 310, that thread must be returned back to the appropriate reservation station 302 or 304 and re-retrieved by arbiter 306 and thereupon provided to the other unit 308 or engine 310, respectively. *Id*. at 4:42–48.

Significantly, the Specification indicates that a thread is provided to a *specific type* of command processing engine (e.g., an ALU or texture engine) based on *the type of operations* (e.g., an ALU or texture operation). *Id.* at 3:62–4:48. ATI's own expert, Dr. Wolfe, testifies that "vertex command can also involve texture operations." Ex. 2151 ¶¶ 159, 165 (noting that "at least 10–20% of vertex command threads involving texture operations should be processed by the texture fetch processor"). Dr. Wolfe also explains that

pixel command threads can involve ALU operations. *Id.* ¶¶ 161–162 (noting "pixel command threads involving ALU operations, which contribute to 20–30% of the ALU operations"). This means that about 10–20% of vertex command threads involving texture operations cannot be processed in the ALU, and 20–30% of pixel command threads involving ALU operations cannot be processed in the texture engine. Put simply, ALU and texture engines are *type-specific* processing engines, and *each* unit or engine cannot process *all* of the threads selected by an arbiter.

Construing the "command processing engines" limitation recited in claim 5 to exclude *type-specific* processing engines, as proposed by ATI, would be inconsistent with the Specification. *Id.* at 2:59–62, 3:62–4:48, Fig. 4. Additionally, ATI's proposed claim construction would be inconsistent with claims 6 and 7, which recite "wherein the plurality of command processing engines comprises at least one arithmetic logic unit" and "at least one texture processing engine," respectively. *Id.* at 8:16–21.

More importantly, ATI's proposed claim construction would import improperly an extraneous negative limitation into the claims—excluding *type-specific* processing engines. *Hoganas AB v. Dresser Indus., Inc.*, 9 F.3d 948, 950 (Fed. Cir. 1993) ("It is improper for a court to add 'extraneous' limitations to a claim, that is, limitations added 'wholly apart from any need to interpret what the patentee meant by particular words or phrases in the claim.""). Such a claim construction would not be reasonable as it would exclude the *very embodiment* that provides written description support for the claims at issue. *See Kaneka Corp. v. Xiamen Kingdomway*

*Group Co.*, 790 F.3d 1298, 1304 (Fed. Cir. 2015) ("A claim construction that excludes a preferred embodiment is rarely, if ever, correct.").

For all of the reasons discussed above, we decline to adopt ATI's proposed claim construction that excludes *type-specific* processing engines and that requires *each* command processing engine to be able to process *all* of the command threads selected by an arbiter. Rather, consistent with the plain meaning of the claim language, we construe the "command processing engine" limitation recited in claim 5 as requiring each command processing engine to be coupled to an arbiter and operable to receive and process a command thread selected by the arbiter.

### B. Antedating Lindholm, Moreton, and Stuttard

LG asserts that each of the following U.S. patents qualifies as prior art under 35 U.S.C. § 102(e)<sup>3</sup> against the challenged claims of the '053 patent, which has an effective filing date of September 29, 2003:

Lindholm filed June 27, 2003 (Ex. 1004, at [22]);

Moreton filed April 21, 2003 (Ex. 1006, at [22]); and

Stuttard filed October 9, 2001 (Ex. 1005, at [22]).

Pet. 10. LG relies upon the U.S. filing dates of these references as the prior art dates under § 102(e). *Id.* Indeed, neither Lindholm nor Moreton claims the benefit of an earlier-filed U.S. application. Ex. 1004, 1; Ex. 1006, 1.

<sup>&</sup>lt;sup>3</sup> Because the '053 patent was filed before the enactment of the Leahy-Smith America Invents Act, Pub. L. No. 112-29, 125 Stat. 284 (2011) ("AIA"), the pre-AIA version of 35 U.S.C. § 102(e) applies in this trial.

Stuttard claims under §§ 120 and 365(c), as a continuation, the benefit of International Application No. PCT/GB00/01332 ("the '332 PCT application"), which was filed on April 7, 2000, and published by the International Bureau in the English language as International Patent Publication No. WO 00/62182 ("the '182 international publication") on October 19, 2000. Ex. 1005, at [63], 1:5–9. The international filing date, April 7, 2000, however, is not a U.S. filing date for prior art purposes under § 102(e) because the '332 PCT application was filed prior to November 29, 2000, the effective date of § 102(e). Therefore, the effective date of Stuttard as prior art is its U.S. filing date, October 9, 2001. See Sun Studs, Inc. v. ATA Equip. Leasing, Inc., 872 F.2d 978, 983 (Fed. Cir. 1989) ("When patents are not in interference, the effective date of a reference United States Patent as prior art is its filing date in the United States, as stated in § 102(e), not the date of conception or actual reduction to practice of the invention claimed or the subject matter disclosed in the reference patent.").

As an initial matter, we note that the '182 international publication also is a prior art reference under § 102(b) because it was published on October 19, 2000, which is more than one year prior to the effective filing date of the '053 patent (September 29, 2003). Ex. 1005, at [63], 1:5–9;

<sup>&</sup>lt;sup>4</sup> See Sections 4505, 4508 of the American Inventors Protection Act of 1999, Pub. L. No. 106-113, 113 Stat. 1501A-552, 565–67 (1999), as amended by the Intellectual Property and High Technology Technical Amendment Act of 2002, Public Law 107-273, 116 Stat. 1158, 1902–03 (2002).

Ex. 3003; Ex. 1001, at [63]. Stuttard and the '182 international publication have the same disclosure given Stuttard was issued as a patent from a continuation application of the '332 PCT application that was published as the '182 international publication. *See Transco Prods. Inc. v. Performance Contracting, Inc.*, 38 F.3d 551, 555 (Fed. Cir. 1994) ("Continuation and 'divisional' applications are alike in that they are both continuing applications based on the same disclosure as an earlier application."). LG, however, did not assert the '182 international publication in any of its grounds of unpatentability.

Here, ATI seeks to disqualify Lindholm, Moreton, and Stuttard as prior art under § 102(e) by establishing a date of invention prior to the U.S. filing dates of these references. PO Resp. 15–29. Section 102(e)(2) requires a prior art patent to have a U.S. filing date "before the invention by the applicant for patent." *See Loral Fairchild Corp. v. Matsushita Elec. Indus. Co., Ltd.*, 266 F.3d 1358, 1362 (Fed. Cir. 2001). In particular, ATI alleges that the named inventors of the '053 patent conceived the claimed subject matter of the '053 patent no later than August 24, 2001, before the filing dates of Lindholm, Moreton, and Stuttard. *Id.* at 22–24, 27. ATI also contends that the named "inventors were reasonably and continuously diligent to reduce the claimed subject matter to practice." *Id.* at 2, 24–26, 28–29. Thus, ATI argues diligence from the date of conception until the constructive reduction to practice of the claimed invention on the filing date of the application that issued as the '053 patent. ATI also argues that the

claimed invention was actually reduced to practice before the filing dates of Lindholm and Moreton. *Id.* at 15–22.

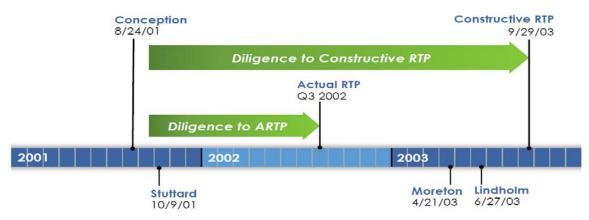

ATI provides the following timeline:

# Antedating Stuttard, Moreton, & Lindholm

Ex. 2155, 3. An inventor "may date his patentable invention back to the time of its conception, if he connects the conception with its reduction to practice by reasonable diligence on his part, so that they are substantially one continuous act." *Mahurkar v. C.R. Bard, Inc.*, 79 F.3d 1572, 1577 (Fed. Cir. 1996).

#### Constructive Reduction to Practice

Constructive reduction to practice occurs when a patent application on the claimed invention is filed. *Weil v. Fritz*, 572 F.2d 856, 865 n.16 (CCPA 1978). On its face, the '053 patent claims under § 120, as a continuation, the benefit of the filing date of U.S. Application 10/673,761, filed on September 29, 2003. Ex. 1001, at [63]. LG does not challenge that the effective filing date of the '053 patent is September 29, 2003. *See generally*

Reply. On this record, we, therefore, determine that ATI's date of constructive reduction practice is September 29, 2003.

## Conception

"Conception must be proved by corroborating evidence which shows that the inventor disclosed to others his completed thought expressed in such clear terms as to enable those skilled in the art to make the invention." *Coleman v. Dines*, 754 F.2d 353, 359 (Fed. Cir. 1985).

Here, ATI alleges that the named inventors conceived the claimed subject matter no later than August 24, 2001, while designing a graphics processing unit known as the R400 Graphics Processing System ("the R400"). PO Resp. 1–3, 7–11, 23–24. ATI relies on Version 0.4 of the R400 Sequencer Specification (Ex. 2010) as evidence of conception. PO Resp. 11. As support, ATI also proffers a Declaration of Mr. Laurent Lefebvre (Ex. 2006), one of the named inventors of the '053 patent, and a Declaration of Dr. Wolfe (Ex. 2106 ¶ 240) to explain how the R400 Sequencer Specification discloses every element of each challenged claim.

LG does not dispute the sufficiency of the R400 Sequencer Specification for showing conception. *See generally* Reply. Based on the evidence before us, we are satisfied with the sufficiency of the documents to show conception, and they also serve as effective corroboration to Mr. Lefebvre's testimony as to establishing conception. Exs. 2006, 2106, 2010, 2028, 2040, 2041. On this record, we, therefore, determine that ATI has demonstrated by a preponderance of the evidence that the named inventors of the '053 patent conceived the claimed system no later than

August 24, 2001, prior to the U.S. filing dates of Stuttard, Moreton, and Lindholm.

## **Actual Reduction to Practice**

In order to establish an actual reduction to practice, the inventor must establish that: (1) the inventor constructed an embodiment or performed a process that met all of the claim limitations; and (2) the invention would work for its intended purpose. *Cooper v. Goldfarb*, 154 F.3d 1321, 1327 (Fed. Cir. 1998). The inventor's testimony must be corroborated by independent evidence. *Id.* at 1330. A rule of reason applies to determine whether the inventor's testimony has been corroborated. *Price v. Symsek*, 988 F.2d 1187, 1194 (Fed. Cir. 1993). "The rule of reason, however, does not dispense with the requirement for some evidence of independent corroboration." *Coleman*, 754 F.2d at 360. The requirement of "independent" corroboration requires evidence other than the inventor's testimony. *In re NTP, Inc.* 654 F.3d 1279, 1291 (Fed. Cir. 2011).

Here, ATI asserts that the register-transfer level ("RTL") code (Exs. 2072–87) in hardware-description language for the R400 is a constructed embodiment of the claimed invention. PO Resp. 3, 16–22. As support, ATI proffers a Declaration of Dr. Wolfe (Ex. 2106) to demonstrate how the RTL code maps to each claim at issue, and a Declaration of Mr. Lefebvre (Ex. 2006) to explain why the first-triangle test shows that the RTL code worked for its intended purpose. PO Resp. 3.

LG counters that ATI fails to provide sufficient evidence to establish that the named inventors constructed a *physical* embodiment because

computer simulations that were never reduced to a physical embodiment cannot serve as an actual reduction to practice. Reply 2–3. LG also alleges that ATI has not shown that its code actually worked for its intended purpose because ATI's evidence shows that the code had a number of problems. *Id.* at 5–7. LG further contends that the evidence does not show the RTL code passed the first-triangle test on July 1, 2002, as the RTL code has a revision date of August 5, 2002, which is after the alleged test. *Id.* at 7; Ex. 2066, 6.

In its Sur-reply, ATI responds that a *physical* embodiment is not required to establish an actual reduction to practice. Sur-reply 2–4 (citing *Cooper*, 154 F.3d at 1328; *Yorkey v. Diab*, 601 F.3d 1279, 1290–91 (Fed. Cir. 2010)). ATI also asserts that the RTL code is an embodiment that discloses every claim element and maps to hardware. *Id.* at 3–4. According to ATI, its evidence shows that the first-triangle test was conducted successfully. *Id.* at 4. ATI cites to Mr. Lefebvre's testimony (Ex. 2006 ¶ 47), and the Program Review Slides (Ex. 2062, 4; Ex. 2066, 2, 6) for support.

# Requirement of a physical embodiment

It is well settled that "[t]here cannot be a reduction to practice of the invention . . . without a *physical embodiment* which includes all limitations of the claim." *UMC Elecs. Co. v. United States*, 816 F.2d 647, 652 (Fed. Cir. 1987) (emphasis added). "It is equally well established that every limitation of the [claim] *must exist* in the embodiment and be shown to have performed as intended." *Newkirk v. Lulejian*, 825 F.2d 1581, 1582 (Fed. Cir. 1987) (emphasis added).

Here, based on the evidence in this trial, we are not persuaded that ATI has demonstrated that the claimed system was actually reduced to practice. In its Patent Owner Response and Sur-reply, ATI does not contend that it constructed a hardware device in accordance with the challenged claims. Nor has ATI established that an implementation based on the RTL code constitutes the subject matter of the challenged claims in this record. At best, ATI has shown that the RTL code constitutes software files in a hardware description language that describes the logical design and behavior of the system. ATI, however, has not demonstrated that the design *inferred* by the RTL code was synthesized into a set of interconnected hardware devices. It is well-established that an *equivalent* of a physical embodiment does not satisfy the first requirement of actual reduction to practice. *Eaton v. Evans*, 204 F.3d 1094, 1097–98 (Fed. Cir. 2000) (holding that a party cannot obviate the first requirement of constructing a physical embodiment through evidence of testing an equivalent).

At the outset, we note that the claims at issue are apparatus claims directed to a *graphics processing system*, and not a *circuit design*, as ATI alleges (Sur-reply 4). *See* Ex. 1001, 7:10–8:28. As Dr. Wolfe testifies, both circuit design and fabrication are necessary components of constructing a physical integrated circuit, commonly referred to as "a chip." Ex. 2106 ¶¶ 32–33. It is undisputed that ATI submits no evidence to show that a sample or prototype for the R400 was fabricated before the filing dates of the asserted references. PO Resp. 7–9; Sur-reply 3–4; Tr. 80:1–3. A *design*, by itself, is not a physical hardware element, let alone a graphics processing

system. Therefore, such a design is insufficient to show an actual reduction to practice of the claimed graphics processing system. *See UMC*, 816 F.2d at 652 ("It is not sufficient for a reduction to practice that [the inventor] built and tested only a part of the later-claimed model UMC-B accelerometer."); *Fitzgerald v. Arbib*, 268 F.2d 763, 765–66 (CCPA 1959) (noting that the reduction to practice of a three-dimensional design invention required the production of an article embodying that three-dimensional design and not a mere drawing); *In re McIntosh*, 230 F.2d 615, 619 (CCPA 1956) (holding that drawings and models could establish only conception, but not actual reduction to practice, because "there is nothing of record to suggest that appellant ever made or tested a full-sized airplane constructed in accordance with any of the appealed claims").

We are not persuaded by ATI's argument that a *physical* embodiment is not required to establish an actual reduction to practice of the recited system. PO Resp. 19–21; Sur-reply 2. ATI's reliance on *Cooper* to support its argument is misplaced. Sur-reply 2 (citing *Cooper*, 154 F.3d at 1328). In fact, *Cooper* specifically quotes *UMC*, which states that "[t]here cannot be a reduction to practice of the invention . . . *without a physical embodiment* which includes all limitations of the claim," and further explains that "the *physical* embodiment relied upon as an actual reduction to practice must include every limitation." *Cooper*, 154 F.3d at 1327 (quoting *UMC*, 816 F.2d at 652; citing *Correge v. Murphy*, 705 F.2d 1326, 1329 (Fed. Cir. 1983)) (emphases added). Moreover, it was undisputed that a physical embodiment was constructed in *Cooper*. The inventor in *Cooper* conducted

successfully a series of experiments with physical embodiments of the claimed artificial vascular graft. *Cooper*, 154 F.3d at 1324 ("The parties agree that a single successful graft in a dog would constitute an actual reduction to practice.").

ATI's reliance on *Yorkey* also is unavailing. PO Resp. 17; Sur-reply 2 (citing *Yorkey*, 601 F.3d at 1290–91). *Yorkey* involved *method claims* directed to a method of measuring saturation of a blood constituent, whereas the instant trial involves *apparatus claims* directed to a graphics processing system comprising an arbiter coupled to a memory device and a plurality of command processing engines. *Yorkey*, 601 F.3d at 1282; Ex. 1001, 7:10–8:28. To show an actual reduction to practice of a claimed apparatus, as here, the inventor must *construct a physical embodiment* that includes all the claimed apparatus elements. *UMC*, 816 F.2d at 652; *Fitzgerald*, 268 F.2d at 765–66; *Correge*, 705 F.2d at 1329 ("The *physical* embodiment relied upon as an actual reduction to practice of the invention . . . must include every essential limitation." (emphasis added)).

Furthermore, in *Yorkey*, it was uncontested that the method was performed successfully in measuring blood oxygen saturation, and the software program implementing the central equation of the eta methodology was tested using data collected from patients in hospitals and in-house clinical studies. *Yorkey*, 601 F.3d at 1287–90. Such circumstances are not present here. In fact, ATI does not contend that the computer system executing the RTL code encompasses the claimed graphics processing system, but rather the RTL code, by itself, which purportedly "defines the

actual hardware of the chip" and serves as "an accurate representation of a hardware chip design," is sufficient as an embodiment to show actual reduction to practice. PO Resp. 8–9, 16–21; Sur-reply 3–4; Ex. 2106 ¶¶ 31, 32. Simply mapping a software code to hardware features is insufficient to show that the hardware features actually existed. *See Newkirk*, 825 F.2d at 1582–83 (noting that proof of actual reduction to practice requires showing that the claimed apparatus features actually existed).

Calling the RTL software code an embodiment or implementation of the claimed system does not change the fact that the claimed hardware elements do not exist. At most, the RTL code represents a logical behavior design from which a hardware implementation can be *inferred*. However, "there can be no actual reduction to practice if the constructed embodiment . . . lacks an element recited in the [claim] or *uses an equivalent of that element*." *Eaton*, 204 F.3d at 1097 (emphasis added). Hence, we do not discern that either *Cooper* or *Yorkey* supports ATI's proposition that no *physical* embodiment is required, or that a "representation of a hardware chip design" constitutes an actual reduction to practice of a physical integrated circuit.

ATI also argues that a *physical* embodiment is not required simply because a *commercially acceptable* embodiment is not required for establishing actual reduction to practice. PO Resp. 19–21; Sur-reply 2–3. ATI, however, conflates the two distinct and separate requirements of actual reduction to practice: (1) constructing a physical embodiment, and (2) testing the embodiment. "An invention is actually reduced to practice

when [1] it is put into *physical form* and [2] shown to be operative in environment of its practical contemplated use." *See Technical Dev. Corp. v. United States*, 597 F.2d 733, 746–47 (Ct. Cl. 1979). For the testing requirement, "[1]aboratory tests, rather than tests under actual use or service conditions, may be sufficient to constitute actual reduction to practice if the conditions of the test adequately simulate the conditions of practical use." *Id.* at 747. However, permitting laboratory test simulation to satisfy the testing requirement does not eliminate the physical embodiment requirement. *See Eaton*, 204 F.3d at 1097; *Wetmore v. Quick*, 536 F.2d 937, 942 (CCPA 1976) (finding that, despite successful testing, there was no actual reduction to practice where the embodiment used an equivalent of an element).

ATI's reliance on *Scott v. Finney* also is misplaced, as the Court in *Scott* was addressing the *testing* requirement. 34 F.3d 1058, 1061 (Fed. Cir. 1994) (noting that actual reduction to practice "does not require that the invention, *when tested*, be in a commercially satisfactory stage of development" (emphasis added)). In *Scott*, there was no dispute that the physical embodiment actually existed. *Id.* at 1059. A videotape showed an operation where the surgeon inserted Dr. Scott's prototype device into an anesthetized patient. *Id.* at 1060–1063. Nothing in *Scott* suggests that a physical embodiment is not required, as alleged by ATI. *Id.* More importantly, in *Eaton*, the Federal Circuit expressly rejected the argument that satisfying the testing requirement eliminates, or acts as a surrogate for, the requirement of constructing a physical embodiment, because such an

argument "misapprehends this Court's precedent and conflates the two requirements." *Eaton*, 204 F.3d at 1098 (holding that a party cannot obviate the first requirement for a physical embodiment through evidence of testing an equivalent, regardless of the quality of such evidence). "Put simply, these are two distinct requirements and a party must satisfy each one to establish an actual reduction to practice." *Id*.

We also are not persuaded by ATI's argument that the inventive process for the claimed invention ended after chip design, "so it is logical that RTL is a valid reduction to practice." IPR2015-00330, Paper 36, Sur-reply 2. This argument squarely contradicts our reviewing Court's precedent that requires a physical embodiment, and that there is no actual reduction to practice if the embodiment is merely an equivalent. Eaton, 204 F.3d at 1097–98; Wetmore, 536 F.2d at 942; Martin v. Snyder, 214 F.2d 177, 180 (CCPA 1954) (holding that doctrine of equivalents does not apply when determining whether a constructed embodiment contained every element of the invention). Moreover, ATI's argument conflates actual reduction to practice with *conception*, which is established when the inventive process ends. See Hybritech Inc. v. Monoclonal Antibodies Inc., 802 F.2d 1367, 1376 (Fed. Cir. 1986) (Conception is the "formation in the mind of the inventor of a definite and permanent idea of the complete and operative invention as it is thereafter to be applied in practice."); Townsend v. Smith, 36 F.2d 292, 295 (CCPA 1930) (defining conception as "the complete performance of the mental part of the inventive act"). As discussed above, actual reduction to practice is established only when the invention "is put

into *physical form* and shown to be operative in environment of its practical contemplated use." *Technical Dev.*, 597 F.2d at 746–47 (emphasis added).

In light of the foregoing, and consistent with our reviewing Court's precedent, we determine that a *physical* embodiment of the claimed graphics processing system is required here, and that a *circuit design*, by itself, is insufficient to establish actual reduction to practice.

ATI does not contend that the computer system executing the RTL code encompasses the claimed graphics processing system, but rather the RTL code, alone, is an embodiment of the claimed system. PO Resp. 7–9, 16–21; Sur-reply 3–4. ATI argues that the entire chip-design industry recognizes that once a chip has been defined in a hardware-description language, as here, "an embodiment of the chip has been constructed." PO Resp. 18–19. ATI alleges that the RTL code "defines the actual hardware of the chip," and, as a result, the RTL code is "an implementation" of the graphic processing unit ("GPU"). *Id.* at 8–9.

We are not persuaded by ATI's argument that the RTL code, alone, is sufficient to meet the first requirement of actual reduction to practice—constructing a *physical* embodiment. PO Resp. 7–9, 16–20; Sur-reply 3–4. At best, the RTL code is a chip design or a software program that represents the logical design behavior of the claimed graphics processing system. As ATI's own expert, Dr. Wolfe, explains, RTL code is "generally used to model, define, and instantiate a hardware design." Ex. 2106 ¶ 23. According to Dr. Wolfe, "[w]hile the design representation at this stage may resemble software, its primary purpose is to be an accurate representation of

a hardware chip design." Id. ¶ 32. Dr. Wolfe also testifies that the "R400 Emulator Code . . . emulates the behavior of the graphics-processing system recited in claims 1, 2, 5, 6, and 7 using software that executes on a computer." Ex. 2106 ¶ 37. Based on Dr. Wolfe's testimony, we observe that the RTL code is merely a representation of a chip design or a software program that emulates the behavior of a physical system that includes hardware elements, but it is not a physical embodiment of that system.

ATI further asserts that it is an integrated circuit design company, so that the actual reduction to practice was in the RTL code. PO Resp. 3. ATI argues that the fabrication phase begins only after the RTL code has been thoroughly tested, and the designer's final product is the RTL code, which is converted into a "GDSII or *tape-out* file and sent to a circuit-fabrication facility." *Id.* at 9 (emphasis in the original). According to ATI, the fabrication process "is very expensive, so a graphics-processing company, such as ATI, will typically tape-out a GPU only if the design is ready for commercialization—meaning that the GPU design has passed hundreds, if not thousands, of tests." *Id.*

ATI's evidence, however, shows that it was scheduled to obtain a sample or prototype of the R400 in May 2002. Ex. 2040, 8. ATI confirms that there was a plan, at the outset, to make a prototype of the chip. Tr. 81:10–16. ATI also acknowledges that "there was actually never a tape out, a sample, or a production for the R400," but ATI did not submit any evidence as to why ATI could not have obtained a prototype of the R400, other than commercially related reasons. Tr. 80:2–11, 82:5–10.

In any event, either allegation that ATI is a chip-design company or that the fabrication phase of making a chip is a very expensive process, even if they were true, does not discharge ATI from satisfying the requirement of constructing a physical embodiment. Eaton, 204 F.3d at 1098; Fitzgerald, 268 F.2d at 765–66. In addition, ATI's arguments are premised improperly on the notion that constructing a physical embodiment would require the inventors to fabricate, personally themselves, a chip with a commercially acceptable design. It is well-settled that a reduction to practice can be done by another on behalf of the inventor. Solvay S.A., v. Honeywell Int'l Inc., 742 F.3d 998, 1000 (Fed. Cir. 2014); In re De Baun, 687 F.2d 459, 463 (CCPA 1982) ("[T]here is no requirement that the inventor be the one to reduce the invention to practice so long as the reduction to practice was done on his behalf."). "Commercially acceptable structure or operation is not necessary for a reduction to practice." Goodrich v. Harmsen, 442 F.2d 377, 383 (CCPA 1971). Furthermore, the inventors had the opportunity to establish constructive reduction to practice by filing a patent application upon conception, avoiding the cost and delay of constructing a physical embodiment of their invention. See Weil, 572 F.2d at 865 n.16; In re Mulder, 716 F.2d 1542, 1545 (Fed. Cir. 1983) (holding that appellants are entitled to rely on their filing date for a constructive reduction to practice); see also Grabowsky v. Gallaher, 39 App. D.C. 548, 551–52 (D.C. Cir. 1913) ("Appellant seeks to excuse this delay by the plea that he was a poor man and did not have the means to actually reduce the invention to practice, which, undoubtedly, would have involved considerable expense. Granting

this to be true, the record fails to show that he was unable to pay the cost of preparing and prosecuting an application, which it was his duty to do."). Here, ATI chose to wait more than two years from conception to file a patent application, while others—Stuttard, Moreton, and Lindholm—filed their applications earlier. *Naber v. Cricchi*, 567 F.2d 382, 385 n.5 (CCPA 1977) ("Public policy favors the early disclosure of invention."); *Gould v. Schawlow*, 363 F.2d 908, 921 (CCPA 1966).

Based on the evidence before us, we determine that ATI has not demonstrated by a preponderance of the evidence that the claimed invention was actually reduced to practice. For the reasons discussed below, even if we were to accept the RTL code as a physical embodiment of the claimed system, we find that ATI fails to provide sufficient evidence in this record to show that the RTL code was tested successfully and adequately to prove that the claimed system would have worked for its intended purpose.

# Testing requirement

To show actual reduction to practice, the inventor also must demonstrate that the claimed invention would work for its intended purpose. *Cooper*, 154 F.3d at 1327. Here, ATI relies on Mr. Lefebvre's testimony (Ex. 2006 ¶¶ 44–52) to show that the RTL code (Exs. 2072–87), submitted as evidence of actual reduction to practice, worked for its intended purpose, and several PowerPoint slides (*e.g.*, Ex. 2066, 2, 6) to corroborate Mr. Lefebvre's testimony. PO Resp. 13–15, 21–22; Sur-reply 1, 4. LG counters that the high-level slides are insufficient corroborating evidence,

and that ATI does not proffer any witness to explain how the slides relate to the claimed elements. Reply 2. On this record, we agree with LG.

We recognize that "some inventions are so simple and their purpose and efficacy so obvious that their complete construction is sufficient to demonstrate workability." *Mahurkar*, 79 F.3d at 1572. "Complex inventions and problems in some cases require laboratory tests that accurately duplicate actual working conditions in practical use," however. *Scott*, 34 F.3d at 1062. "[T]he testing requirement depends on the particular facts of each case, with the court guided by a common sense approach in weighing the sufficiency of the testing." *Id.* at 1061. Commercial perfection or absolute replication of the circumstances of the claimed invention's ultimate use is not required. *Id.* at 1063. "Laboratory tests, rather than tests under actual use or service conditions, may be sufficient to constitute actual reduction to practice if the conditions of the test adequately simulate the conditions of practical use." *Technical Dev.*, 597 F.2d at 747; *Elmore v. Schmitt*, 278 F.2d 510, 513 (CCPA 1960).

Here, ATI does not assert that the claimed graphics processing system is so simple that it needs no testing to show actual reduction to practice. PO Resp. 13–15. Rather, ATI asserts that, "[t]o validate the R400 design and before a tape-out could occur, the design had to pass hundreds, if not thousands, of tests." *Id.*; Ex. 2006 ¶ 47. In the context of the '053 patent, we agree with ATI that testing is required to show that the claimed system would work for its intended purpose, but, on this record, we do not find that

there is sufficient evidence to show that the claimed invention would work for its intended purpose.

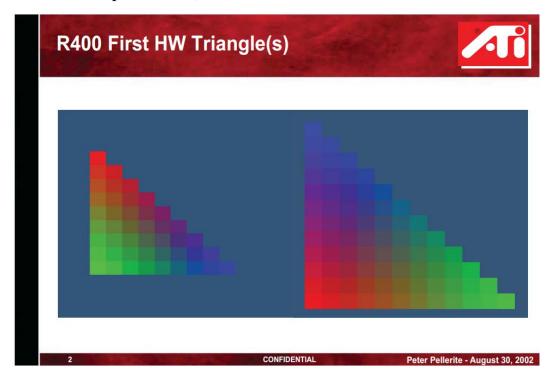

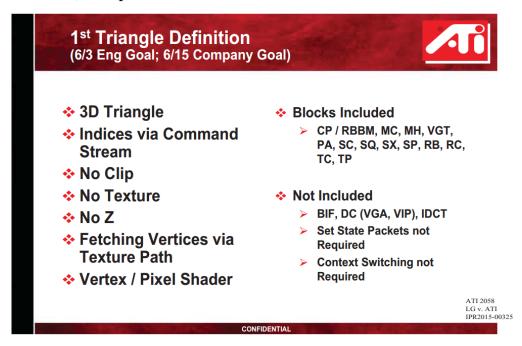

Mr. Lefebvre testifies that the R400 team developed the C++ emulation code and RTL code for the various blocks of the R400, and the code was tested extensively on individual blocks and the entire graphics core during the development process. Ex. 2006 ¶¶ 44–46. Yet, Mr. Lefebvre and ATI direct our attention to only one reported result of a "first triangle" test, which was allegedly conducted on July 1, 2002. *Id.* ¶¶ 44–49; PO Resp. 13–15, 21–22. That report is provided in the form of two high-level PowerPoint slides, reproduced below with a green marking added (Ex. 2066, 2, 6; Ex. 2155, 27; Papers 63, 64).

| Task                                                   | Plan     | Actual   | Forecast |

|--------------------------------------------------------|----------|----------|----------|

| Significant Architecture Issue Identification Complete | 10-15-01 | 10-10-01 |          |

| Emulator Test template Complete                        | 01-18-02 | 01-18-02 |          |

| GC Emulator integration – 1 triangle                   | 02-22-02 | 02-21-02 |          |

| Core Emulator pixel / shader tests run                 | 03-15-02 | 03-19-02 |          |

| Block Testing Begins                                   | 04-16-02 | 05-01-02 |          |

| GC/Chip Integration Start                              | 05-17-02 | 05-15-02 |          |

| Simulate 1 Triangle / Emulator ready for SW            | 06-15-02 | 07-01-02 |          |

| First Syntheses                                        | 07-12-02 | 08-03-03 |          |

| Verilog Feature Complete                               | 09-16-02 |          | 09-30-02 |

| IKOS Emulation start                                   | 10-11-02 |          | 10-11-02 |

| Begin early block delivery                             | 11-08-02 |          | 11-15-02 |

| IKOS Emulation (w/ Software) begins                    | 11-11-02 |          | 11-11-02 |

| RTL Freeze / Final Netlist (Gate level ECO only)       | 11-15-02 |          | 12-15-02 |

| A11 Base Layers Tapeout                                | 01-10-03 |          | 02-14-03 |

| A11 Metal Layers Tapeout                               | 01-24-03 |          | 02-28-03 |

| First Samples for Engineering                          |          |          | 05-09-03 |

| A12 Tapeout                                            |          |          | 06-14-03 |

| A12 Samples for Engineering                            |          |          | 07-12-03 |

| R400 Customer Samples                                  |          |          | 07-19-03 |

| Volume Ramp                                            |          |          | 08-19-03 |

| Product Delivery                                       |          |          | 09-01-03 |

Slide 2 shows two triangles with a heading "R400 First HW Triangle(s)" and Slide 6 is a high-level program schedule, which states, in part, "Simulate 1 Triangle / Emulate ready for SW" for the July 1, 2002 entry under the "Actual" column. *Id.* The slides are silent as to what was tested, how the triangles were generated, and what software program or computer system generated the triangles. Significantly, the slides do not indicate whether the key claimed elements were tested—e.g., what priority scheme, if any, was tested; how many command processing engines, if any, were tested; or whether each command process engine was tested to demonstrate that it can execute a pixel or vertex command thread.

The slides are said to be a part of Mr. Peter Pellerite's presentation. Sur-reply 4. Yet, ATI did not submit a declaration from Mr. Pellerite, or anyone else who could explain meaningfully what these slides purportedly show. Nor does its expert, Dr. Wolfe, testify that he executed the RTL code and that the code actually worked. Ex. 1020, 305:11–22. In sum, the slides provide insufficient detail as to whether the RTL code actually passed the "first triangle" test. *See Newkirk*, 825 F.2d at 1583 ("Proof of actual reduction to practice requires more than theoretical capability.").

Mr. Lefebvre testifies that "I recall the first triangle test being successful approximately mid-way through the R400 project. Consistent with my memory, the PowerPoint slide shows that the first triangle was reported during a meeting on August 30, 2002." Ex. 2006 ¶ 49. Mr. Lefebvre also testifies that "[a]ccording to this presentation, the first triangle was completed on July 1, 2002." Id. However, Mr. Lefebvre's testimony is vague and conclusory, and is not corroborated with independent evidence. ATI's declarant, Mr. Watson, testifies that the files submitted as Exhibits 2072–2104 and 2108, which contain the RTL code and the emulator code, have a revision date of August 5, 2002. Ex. 2105 ¶ 132. According to ATI, the RTL code for R400 was not completed until October 31, 2002. PO Resp. 14–15; Ex. 2068, 1; Ex. 2069, 6; Ex. 2071, 7. It is unclear whether the particular RTL code with a revision date of August 5, 2002 (Exs. 2072–87), submitted as evidence of actual reduction to practice, is the same code that allegedly passed the "first triangle" test on July 1, 2002. ATI proffers insufficient explanation or credible evidence to show that they are the same code. As discussed above, the high-level PowerPoint slides (Ex. 2066, 2, 6) that both ATI and Mr. Lefebvre rely upon do not identify which software program or computer system generated the triangles. ATI fails to provide sufficient independent evidence to corroborate Mr. Lefebvre's testimony that the RTL code passed the "first triangle" test on July 1, 2002, and, therefore, Mr. Lefebvre's testimony is entitled to little, if any, weight. *See NTP*, 654 F.3d at 1291; *Mahurkar*, 79 F.3d at 1577 (noting that the requirement for corroboration of inventor's testimony arose out of a concern that inventors testifying at trial would be tempted to remember facts favorable to their case by the lure of protecting their patent or defeating another's patent).

More importantly, neither ATI nor Mr. Lefebvre proffers any meaningful test results, test input or output files, simulation run logs, or input test parameters, which a person with ordinary skill in the art would have expected to see for testing. Ex. 2153, 112:2–14. At a minimum, ATI's evidence must show "the conditions of the test adequately simulate the conditions of practical use." *Technical Dev.*, 597 F.2d at 747. As discussed above, the picture of two triangles and high-level program schedule do not support that the RTL code was tested successfully to establish that the claimed graphics processing system would work for its intended purpose. *See McDonnell Douglas Corp. v. United States*, 670 F.2d 156, 161 (Ct. Cl. 1982) (Proof of actual reduction to practice must show "that the invention will perform its intended function beyond a probability of failure.").

In his declaration, Mr. Lefebvre also mentions other tests. Ex. 2006 ¶¶ 44–47 ("We ran many tests on the R400 during its development. . . . This code was tested extensively . . . . Tests could be run on both the emulation

code and the RTL code, and these tests could be run on individual blocks or the entire graphics core."). Again, Mr. Lefebvre's testimony is vague and is not corroborated sufficiently with independent evidence. There is no evidence in this record that those other tests were conducted successfully. As such, Mr. Lefebvre's testimony is entitled to little, if any, weight. *See NTP*, 654 F.3d at 1291; *Mahurkar*, 79 F.3d at 1577.

The PowerPoint presentation slides cited by ATI are too general, showing high-level schedules and general descriptions of the "first triangle" test. PO Resp. 13–15, 21–22; Ex. 2057, 6, 9; Ex. 2061, 2–5; Ex. 2062, 4; Ex. 2025, 5; Ex. 2071, 7.

For example, one of the PowerPoint presentation slides (Ex. 2058, 1; Papers 63, 64) is reproduced below:

This high-level slide does not show any test results, test input or output files, simulation run logs, or input test parameters. ATI's evidence

does not provide sufficient detail or explanation to demonstrate that the testing would simulate actually the characteristics and environment of an operative graphics processing system in its practical, contemplated setting. *See Technical Dev.*, 597 F.2d at 747–48; *Elmore*, 278 F.2d at 513; *McDonnell Douglas*, 670 F.2d at 162 ("Tests which fail to simulate the varying and multiple conditions of the invention's intended environment will not serve to prove the operability, stability and reliability of the invention for practical use."). ATI's evidence as a whole is insufficient to establish that the RTL code was tested successfully or adequately to show that the claimed system would work for its intended purpose. *See Gordon v. Hubbard*, 347 F.2d 1001, 1007 (CCPA 1965) (finding the evidence as a whole insufficient to establish actual reduction to practice when it "simply relates that tests were performed, and gives no definite indication or suggestion what results were attained or the results were satisfactory").

In his Declaration, Mr. Lefebvre also provides an example as to how the RTL code arbitrates between vertices and pixels. Ex. 2006 ¶¶ 50–51. However, the code alone does not necessarily show that it would accurately reproduce the operating conditions in which the claimed graphics processing system would be encountered in practical use. As discussed above, ATI acknowledges that, "[t]o validate the R400 design and before a tape-out could occur, the design had to pass hundreds, if not thousands, of tests." PO Resp. 13; Ex. 2006 ¶ 47. Without a sufficient showing of a successful test, the RTL code, by itself, does not demonstrate adequately that the claimed system would work for its intended purpose.

In addition, as LG points out, ATI's evidence indicates that there were significant problems in the code. Reply 5–7. For example, the entry on August 26, 2002, in an ATI document log, indicates that the code had a clamping problem that produced a degenerate triangle. Ex. 2048, 50. Mr. Lefebvre explains that a "degenerate triangle is a triangle that has all three vertices along the same axis, so basically transforms the area into a zero area triangle and makes the triangle disappear." Ex. 1035, 151:19-152:5. ATI's logs reveal this clamping problem was still an issue in February 2003. Ex. 2048, 31–32 ("Fixing clamping problem in the emulator."). As additional examples, the document logs for the sequencer's source code indicate the following problems: (1) the entry on July 15, 2002, stating "[f]ixed the event interface in the SQ [sequencer] . . . which was then crashing the numerical library" (Ex. 2048, 54); (2) the entry on August 5, 2002, stating "[f]ixed a parameter generation bug in SQ [sequencer] which was causing the emulator to crash" (id. at 52); (3) the entry on August 26, 2002, stating "[f]ixed 3 bugs in the HW accurate interpolators," which was causing two triangle tests to fail (id. at 50); (4) the entry on January 7, 2003, stating "[f]ound a major bug in the SQ [sequencer]" (id. at 36); (5) the entry on June 19, 2003, stating "this was causing a failure on a WQL test" and "[t]his was causing r400sx\_wrapper \_01.ccp to fail (this is a test that I wrote to duplicate the WQL test that was failing in order to run it on HW)" (id. at 21); and (6) the entry on November 11, 2003, stating "[t]hese shaders were all broken because the address register was not refreshed prior to use" (Ex. 2052, 46). In June 2003, one of ATI's engineers made a change to the

connection between the SX block and the SQ and explained that he was "not sure how this was working at all with the live SX" beforehand. Ex. 2049, 57. On October 8, 2003, an engineer "[a]dded needed include files" and remarked that it was "[s]trange how these compiled before this." *Id.* at 35. Mr. Vargas also testifies that the version of the code provided by ATI for his review may not have been able to pass a triangle test, noting that the comments in the RTL code indicate that there were known problems. Ex. 1013 ¶¶ 43–47 (citing Ex. 2072, 38:7, 42:11; Ex. 2078, 2:1–4; Ex. 2080, 20:17–18; Ex. 2081, 2:1–4). Although Dr. Wolfe testifies that the RTL code maps to each claimed element, Dr. Wolfe did not testify that he executed the RTL code and that the code actually worked. Ex. 1020, 305:11–22.

In its Sur-reply, ATI does not provide sufficient explanation or credible evidence as to why a code that forms a degenerate triangle would be considered to have passed the "first triangle" test. Rather, ATI responds that the comments identified by LG are related to the emulator code—the code that ATI does not rely on for its actual reduction to practice. Sur-reply 4. Dr. Wolfe, however, testifies that chip "designers would ordinarily use the emulator code such as this to design the integrated circuits as part of their design process." Ex. 2106 ¶¶ 38, 142. ATI confirms that the emulator code "can be tested in a simulated environment to determine whether the GPU design functions properly and is, therefore, an important first step in the GPU design process." PO Resp. 8. ATI further relies on the development and testing of the emulator code, as activities that were directed toward actual reduction to practice of the claimed system, to establish reasonable

diligence. *Id.* at 24–26. In light of the evidence before us, we are not persuaded that the RTL code, without testing, establishes that the claimed system would work for its intended purpose.

We have considered ATI's evidence in this record. We, however, are not persuaded that the evidence as a whole supports that the RTL code submitted by ATI, as evidence of actual reduction to practice (Exs. 2072–87), was tested successfully under conditions that adequately simulate the conditions of practical use. *McDonnell Douglas*, 670 F.2d at 163 (indicating that no reduction to practice until physical tests showed capability of actually working). For the foregoing reasons, even if we were to accept ATI's proposition that the RTL code is a physical embodiment of the claimed system, we determine that ATI fails to demonstrate by a preponderance of the evidence that the RTL code was tested successfully to show that the claimed system would work for its intended purpose.

## Reasonable Diligence

"The reasonable diligence standard balances the interest in rewarding and encouraging invention with the public's interest in the earliest possible disclosure of innovation." *Griffith v. Kanamuru*, 816 F.2d 624, 626 (Fed. Cir. 1987). During the period in which reasonable diligence must be shown, there must be continuous exercise of reasonable diligence. *McIntosh*, 230 F.2d at 619; *see also Burns v. Curtis*, 172 F.2d 588, 591 (CCPA 1949) (referring to "reasonably continuous activity"). A party alleging diligence must account for the entire critical period. *Griffith*, 816 F.2d at 626. Even a short period of unexplained inactivity is sufficient to defeat a claim of

diligence. *Morway v. Bondi*, 203 F.2d 742, 749 (CCPA 1953); *Ireland v. Smith*, 97 F.2d 95, 99–100 (CCPA 1938).

To satisfy the reasonable diligence requirement, "the work relied on must ordinarily be directly related to reduction to practice of the invention." Naber v. Cricchi, 567 F.2d 382, 385–86 (CCPA 1977) (citing Anderson v. Scinta, 372 F.2d 523 (CCPA 1967); Gunn v. Bosch, 181 USPQ 758 (BPAI 1973); Moore v. Harris v. Hale, 92 USPQ 187 (BPAI 1951)) (holding that the work done directed at improving oxide and nitride layer deposition techniques generally applicable to all MNOS devices, not merely the drainsource protected device of the claimed invention, did not satisfy the requirement of reasonable diligence). The work done directed to the *generic* invention cannot be relied upon as evidence of diligence for the specific claimed invention. In re Nelson, 420 F.2d 1079, 1081 (CCPA 1970) ("[W]e must consider the evidence only as it relates to the specific invention claimed."). A party alleging diligence must provide corroboration with evidence that is specific both as to facts and dates. Gould, 363 F.2d at 920; Kendall v. Searles, 173 F.2d 986, 993 (CCPA 1949). The rule of reason does not dispense with the need for corroboration of diligence that is specific as to dates and facts. Gould, 363 F.2d at 920; Kendall, 173 F.2d at 993; Coleman, 754 F.2d at 360.

Here, ATI bears the burden of production in antedating the asserted references. *See Dynamic Drinkware, LLC v. Nat'l Graphics, Inc.*, 800 F.3d 1375, 1378–80 (Fed. Cir. 2015). ATI acknowledges that it must establish reasonable diligence from just before each reference's filing date until its

own constructive reduction to practice, September 29, 2003, because we determine that ATI did not meet its burden of establishing actual reduction to practice. PO Resp. 27. As discussed above, ATI's conception date is August 24, 2001, which predates Stuttard's filing date (October 9, 2001), Moreton's filing date (April 21, 2003), and Lindholm's filing date (June 27, 2003). *Id.* at 24–29. Accordingly, ATI must establish reasonable diligence for the following three critical periods:

<u>Critical Period 1</u> – from just before Stuttard's filing date, October 9, 2001, to September 29, 2003;

<u>Critical Period 2</u> – from just before Moreton's filing date, April 21, 2003, to September 29, 2003; and

<u>Critical Period 3</u> – from just before Lindholm's filing date, June 27, 2003, to September 29, 2003.

To establish reasonable diligence during all three critical periods, ATI relies upon a Declaration of Mr. Lefebvre (Ex. 2006), and the metadata in document logs and folder histories (Exs. 2048–52, 2107) to show that over 100 project managers and designers worked every non-holiday business day to reduce the claimed system to practice. PO Resp. 11–13, 24–26, 28–29. As support, Mr. Lefebvre provides a calendar (Ex. 2006, Part V, 31–56) to show that at least one person on the R400 project team worked on the R400 design every non-holiday business day from August 24, 2001 until September 29, 2003. Ex. 2006 ¶ 42, Part V; Exs. 2048–52, 2107. The calendar references the following document logs and folder histories: R400 Sequencer Emulator Folder History (Ex. 2048, "Em."); R400 Sequencer

Parts Folder History (Ex. 2049, "Parts"); R400 Document Library Folder History (Ex. 2050, "Lib."); R400 Architecture Folder History (Ex. 2051, "Arch."); R400 GFX Testing Folder History (Ex. 2052, "Test"); and R400 Shader Pipe Parts Folder History (Ex. 2107, "SP Parts"). Ex. 2006, 31.

In its Reply, LG counters that ATI's calendar (Ex. 2006, Part V, 31–56) is directed to the entire R400 project, and not simply the claimed system of the '053 patent. Reply 8–9. LG notes, for example, the GFX Testing Folder History (Ex. 2052) includes all of the tests on the R400 project, and ATI failed to parse out which tests were related to the blocks that allegedly embody the claims and which tests related only to other blocks. *Id.* at 11. According to LG, "ATI's work for an entire graphics chip containing numerous subparts wholly unrelated to these features cannot establish diligence." Reply 9.

In response, ATI disagrees, asserting that the project team could not test the sequencer in isolation, which was the "heart of the chip" and "there was no way to apply the correct stimulus on just the sequencer." Sur-reply 5. ATI also submits that at least one document was checked in every business day during the critical periods, and the metadata associated with each check-in date describes the work that occurred. *Id*.

Upon consideration of the evidence in this entire record, we agree with LG. ATI's calendar, metadata, document logs, and folder histories (nearly 1,300 pages) are not self-explanatory and do not explain meaningfully as to which tasks are reasonably necessary for reducing the claimed elements to practice, and which tasks are directed toward

developing and testing other chip designs and optional features. Ex. 2006, Part V, 33–56; Exs. 2048–52, 2107. Moreover, Mr. Lefebvre's testimony, the only testimony that attempts to explain the work ATI relies upon in support of establishing reasonable diligence, is vague and not sufficiently corroborated by independent evidence. Ex. 2006 ¶¶ 41–43 ("This metadata also shows work on the design and development of the R400 generally."). "Mere work does not necessarily constitute diligence." *Gunn*, 181 USPQ at 761. To satisfy the reasonable diligence requirement, the work relied on must be directed toward, or reasonably necessary for, the reduction to practice of the claimed system. *See Naber*, 567 F.2d at 385.

We are not persuaded by ATI's contention that the work allegedly performed for the entire R400 project satisfies the reasonable diligence requirement. As discussed below, the work done for the entire R400 project includes developing and testing other chip designs and optional features to improve graphic processing systems generally, and not merely for the claimed elements. ATI's general allegation that the sequencer, shader, and texture blocks could not be worked and tested in isolation, or the sequencer was "the heart of the chip," does not explain sufficiently why the work performed on other chip designs and optional features was reasonably necessary for the reduction to practice of the claimed system. PO Resp. 11–12; Sur-reply 5. That allegation also squarely contradicts ATI's own evidence, showing that block level testing can be conducted—e.g.,

Mr. Lefebvre testifies that "[t]ests could be run on both the emulation code and the RTL code, and these tests could be run on individual blocks or the

entire graphics core." Ex. 2006 ¶¶ 44–47; *see also* Ex. 2056, 14 ("Tests from block level tests"); Ex. 2069, 8 ("Block Level Test Status"); Ex. 2049, 57 ("2003/07/01 by llefebvr . . . Now works on the SQSP testbench.").

Notably, ATI's evidence shows that the R400 project included developing and testing other chip designs: R200 (Ex. 2057, 7–10, 12–14), RV250 (id. at 11, 15), R300 (id. at 11, 13, 15), and RV450 (id. at 3, 16, 17). See also Ex. 2039, 5 ("Adding R500 modifications."); Ex. 2041, 6 ("The R450, aimed at a volume high end market."); Ex. 2048, 26 ("Neede[d] to validate load on the R500"); Ex. 2050, 359 ("Updated Appendix for delta between R300 and R400"), 391 ("R300 figures showing the wrapping policies"); Ex. 2059, 6 ("R300 Bring up"); Ex. 2061, 9 ("Entire SC Team consumed for 2 weeks for R300 Hangs (not yet resolved)"). Yet, ATI includes all of the activities for the entire R400 project, as evidence of reasonable diligence, without specifically explaining which activities are directed toward reducing the claimed elements to practice, and which activities are directed toward developing and testing other chip designs. Nor does ATI explain why activities that are directed toward the other chip designs are reasonably necessary for the reduction to practice of the claimed elements, which allegedly are embodied only in the R400 design (PO Resp. 11). In light of the foregoing, we determine that ATI fails to provide evidence that is specific both as to facts and dates for each of the three critical periods, during which diligence is required. Gould, 363 F.2d at 920; *Kendall*, 173 F.2d at 993.

Additionally, ATI relies on the first design of R400, as described in Version 0.4 of the R400 Sequencer Specification (Ex. 2010), to establish conception of the claimed invention as of August 24, 2001. PO Resp. 27; Tr. 48:20–49:12. According to ATI, this first design describes all of the claimed elements. PO Resp. 11; Tr. 49:2–4 (This first design "shows that the inventors conceived of the claimed invention, everything that is required for the claimed invention."). Notwithstanding that, Mr. Lefebvre redesigned the R400, after the conception date, to include an optional feature that is not recited in the claims at issue—a sequencer that is capable of processing an unlimited number of clauses. PO Resp. 12–13; Ex. 2006 ¶ 15. Mr. Lefebvre explains that "Microsoft wanted the sequencer to be able to run shaders with an unlimited number of clauses/instructions." Ex. 2006 ¶ 30. According to ATI, the reason for the redesign was Microsoft asked "for more general purpose – longer-living model." PO Resp. 12; Ex. 2060, 5. ATI's activities appear more in the nature of commercial development, which is not accepted as an excuse for delay. See Griffin, 816 F.2d at 627; Fitzgerald, 268 F.2d at 766 ("It is well settled that efforts to exploit an invention commercially do not constitute diligence in reducing it to practice."); Naber, 567 F.2d at 385– 86 (rejecting the proposition that the reasonable diligence requirement was satisfied, notwithstanding delay due to general work on layer deposition techniques needed to produce a commercially-acceptable device).

ATI's evidence indicates that during the time period between August 24, 2001, and April 19, 2002, Mr. Lefebvre was working on the second chip design to include the optional feature. Ex. 2006 ¶¶ 14, 15;

Exs. 2010, 2028; Ex. 2039, 4 ("Changed the interfaces to reflect the changes in the SP," and "Changed the spec to reflect the new R400 architecture."). ATI also acknowledges that "the evidence goes to both designs and more than both designs." Tr. 51:18–19. Therefore, merely stating that the metadata shows "work on the design and development of the R400 generally" and that "over 100 ATI project managers and designers worked on the R400 project every non-holiday business day" does not satisfy ATI's burden of production. Ex. 2006 ¶¶ 41–42; PO Resp. 28–29. The work done that is directed to the second design for a commercially-acceptable device does not constitute reasonable diligence in reducing the claimed elements to practice. See Naber, 567 F.2d at 385–86; Nelson, 420 F.2d at 1081; Fitzgerald, 268 F.2d at 766. This time period overlaps with Critical Period 1 by at least six months—from just prior to Stuttard's filing date, October 9, 2001, to April 19, 2002. Without a meaningful explanation as to which activities listed in the metadata are directed to the second chip design and which activities are directed to reducing the claimed elements to practice, ATI fails to provide a sufficient account or adequate facts to support a showing of the continuity of activities required for reasonable diligence during the entire Critical Period 1. See Rieser v. Williams, 255 F.2d 419, 424 (CCPA 1958) (finding that there was no showing of diligence where no activity was shown during the first thirteen days of the critical period).

According to the R400 Architecture Proposal (dated November 13, 2000), the R400 was scheduled to "tape-out" by April 2, 2002, for fabricating of the chip, "samples" in May 2002, and "production" in

November 2002. Ex. 2040, 8. The R400 Top Level Specification (dated March 11, 2001) also states the "tape-out" for the R400 was scheduled to occur in July 2002. Ex. 2041, 6. Significantly, ATI's evidence indicates at least a delay of nearly eight months due to the redesigning for the optional feature—comparing Version 0.4 of the R400 Sequencer Specification (dated August 24, 2001) describing the first design, with Version 2.0 of the R400 Sequencer Specification (dated April 19, 2002) describing the second design. In fact, Mr. Lefebvre testifies during cross-examination that "the R400 project itself never got taped out." Ex. 1035, 70:20–21. Yet, ATI does not explain sufficiently why implementing the optional feature is reasonably necessary for reducing the claimed elements to practice. *See Griffith*, 816 F.2d at 626 ("The correct inquiry is . . . whether it is reasonable for [the inventor] to require the public to wait for the innovation, given the well settled policy in favor of early disclosure.").

Additionally, the R400 Architecture Proposal (Ex. 2040) and the R400 Top Level Specification (Ex. 2041) indicate that the R400 includes other optional features that are not recited in the challenged claims of the '053 patent—e.g., "nearly transparent dual chip," features for supporting "dual monitor," and a single programmable pipeline that is used for 2D video, 3D vertex, and 3D pixel operations. Exs. 2040, 2041. These documents also reveal that the R400 project includes work for improving other optional features of the prior design, the R300. *See* Ex. 2040, 7 ("We want to further improve the anti-aliasing used in the R300 by reducing the needed memory, and possibly increasing the number of samples per pixel.

The goal is more than fifty percent of the performance and less than three times the memory of anti-aliased rendering. We should also look into improved methods."), 8 ("I would still like to aim for 2x the internal processing capability of the R300"). As ATI's documents describe, the optional features increased costs and delays. *See*, *e.g.*, Ex. 2040, 6 ("To be able to address the very high end desktop/enthusiast market we will support a glueless two chip design instead of a 256 bit bus. . . . There will be costs added to the base chip to support this. Design time, pins, and area will be impacted by adding this support."), 13 ("Since we support dual monitor, this [total bandwidth requirement] is doubled."); Ex. 2041, 7.

It is well settled that "[d]elays in reduction to practice caused by an inventor's efforts to refine an invention to the most marketable and profitable form have not been accepted as sufficient excuses for inactivity." *Griffin*, 816 F.2d at 627; *Schweyer v. Thomas*, 68 F.2d 953 (CCPA 1934) (explaining that efforts toward commercial exploitation of an invention not yet reduced to practice do not constitute diligence); *see also Naber*, 567 F.2d at 385 (holding that, as "there need not be commercial utility to have a reduction to practice," the inventor cannot rely on the work related to layer deposition techniques, which was required to produce a "useful device," rather than a "mere laboratory device"). On this record, ATI does not explain adequately why developing and testing those optional features were reasonably necessary for reducing the claimed elements to practice. Nor does ATI explain why the team of engineers and designers could not have designed, built, and tested a chip embodying the claimed elements, without

those optional features. *See Naber*, 567 F.2d at 385 (noting that it is the inventor's burden to reconcile the waiting period with the reasonable diligence requirement).

Mr. Lefebvre testifies that he and his colleagues worked to implement the design for the R400 by updating the R400 Sequencer Specification, and by developing, testing, and debugging the emulation code and RTL code, including other components that supported and interacted with the sequencer. Ex. 2006 ¶¶ 34–43; Exs. 2007, 2009–2018, 2020–2039. Mr. Lefebvre also testifies that the "metadata shows work that was necessary for implementing the R400 design," and "we could not work on or test the sequencer block or the shader pipe block in isolation." Ex. 2006 ¶ 42. Once again, Mr. Lefebvre's testimony is too general and conclusory.

As discussed above, ATI's evidence shows that the R400 project involves other chip designs and optional features that are not recited in the claims at issue. Yet, Mr. Lefebvre does not explain meaningfully and specifically which activities listed in the metadata are directed to the reduction to practice of the claimed elements and which activities are directed to developing and testing other chip designs and optional features. Instead, Mr. Lefebvre relies upon a calendar and metadata (nearly 1,300 pages) for the entire R400 project (Ex. 2006, 31–56; Exs. 2048–52, 2107), without identifying specific facts and dates as to the particular work that was reasonably necessary for reducing the claimed features to practice. *See Gould*, 363 F.2d at 920; *Kendall*, 173 F.2d at 993. Such evidence fails to corroborate Mr. Lefebvre's testimony for establishing that the R400 team

performed reasonably continuous activities to reduce the claimed system to practice for each of the three critical periods during which diligence is required. As a result, Mr. Lefebvre's testimony (Ex. 2006 ¶¶ 34–43) is entitled to little, if any, weight. *See NTP*, 654 F.3d at 1291.

According to ATI, the RTL code for the R400 design was completed by October 31, 2002. PO Resp. 15; Ex. 2071, 7. ATI submitted thirty-one versions of the R400 Sequencer Specification (Exs. 2007, 2009–18, 2020– 39), but the last version is dated on May 1, 2003. Ex. 2039, 5; Ex. 2006 ¶ 36. ATI also proffered nineteen versions of the R400 program review slide presentations (Exs. 2053–2071), but the last version is dated on November 12, 2002, which states that the first samples or prototype was scheduled for June 25, 2003 (Ex. 2071, 7). As discussed above, ATI confirms that there was a plan, at the outset, to make a prototype of the R400. Tr. 81:10–16. ATI also acknowledges that "there was actually never a tape out, a sample, or a production for the R400," but ATI did not submit any evidence as to why ATI could not have obtained a prototype of the R400, other than commercially related reasons. Tr. 80:2–11, 82:5–10. However, "efforts to exploit an invention commercially do not constitute diligence in reducing it to practice." Fitzgerald, 268 F.2d at 766; Griffin, 816 F.2d at 627; *Naber*, 567 F.2d at 385–86.

On this record, ATI does not provide sufficient explanation or credible evidence that is specific both as to facts and dates, regarding what particular work was done during the time period between June 25, 2003, and September 29, 2003, that is directed toward, or reasonably necessary for, the